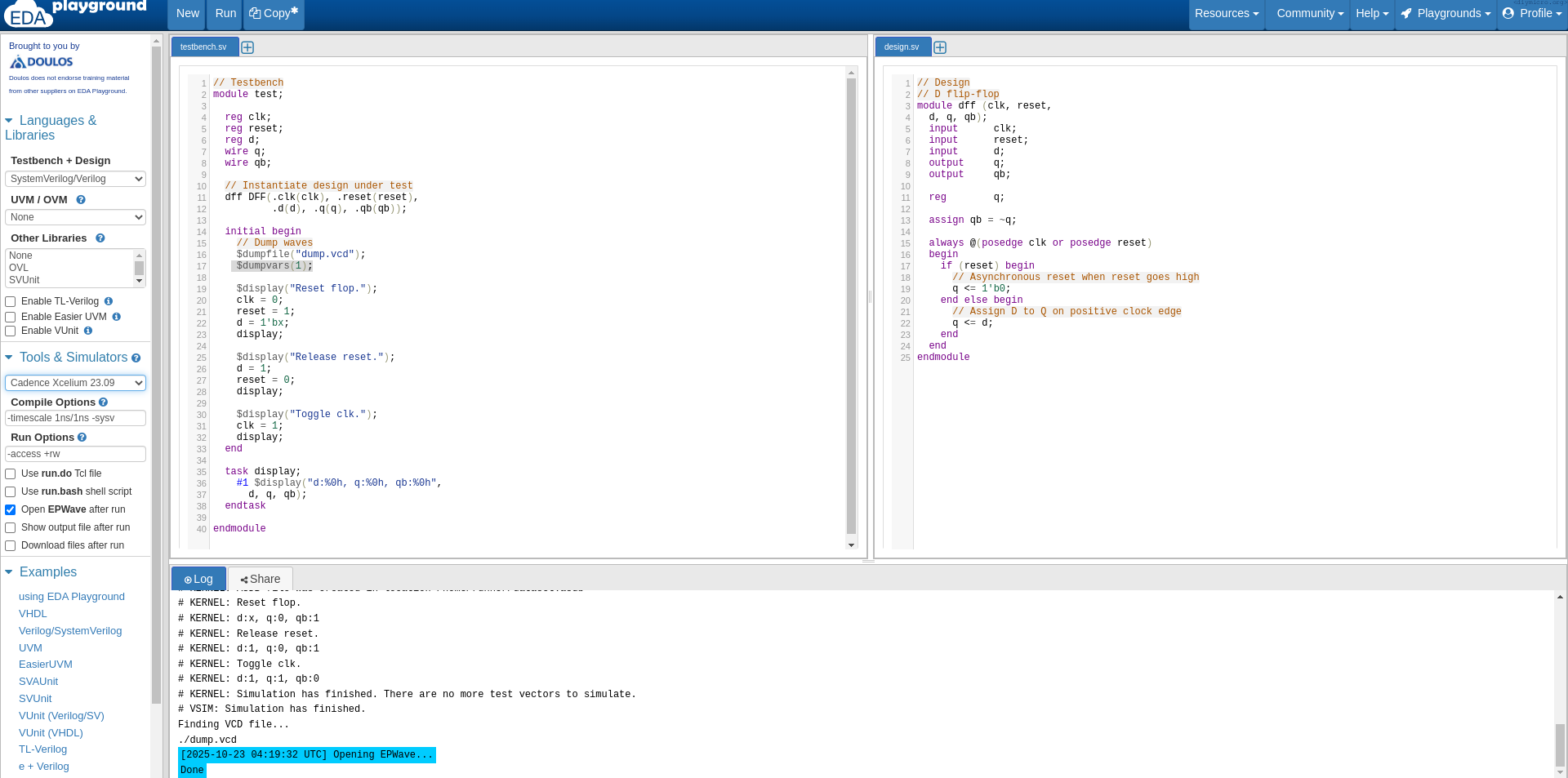

I am not going to explore ton of different tools, at some point I found EDA playground website and it worked quite well for me. So this is a deal, we will use that for online quick tests. Note: you will need to use a working email for a free account.

I prefer to use xcelium simulator since it align with xrun command we use in cadence. They start the sim screen from two code windows: left one for the testbench and the right one for the block itself, though I did not get why do we need it, you can as well add new tab as new file or describe a new module right inside of the testbench code.

!!! Be careful with the stop time in xcelium, apparently there is no explicit way to run simulation for a given time and you need to specify $finish in the initial block to make it stop.

design:

//sandbox design diymicro

module dff (clk, d, q, qb);

input clk;

input d;

output q;

output qb;

reg q;

assign qb = ~q;

initial begin

q = 1'b0;

end

always @(posedge clk)

begin

// Assign D to Q on positive clock edge

q <= d;

end

endmodule

module and_gate (input wire a,b,

output wire z);

assign z = a & b;

endmodule

module or_gate (input wire a,b,

output wire z);

assign z = a | b;

endmoduleand testbench

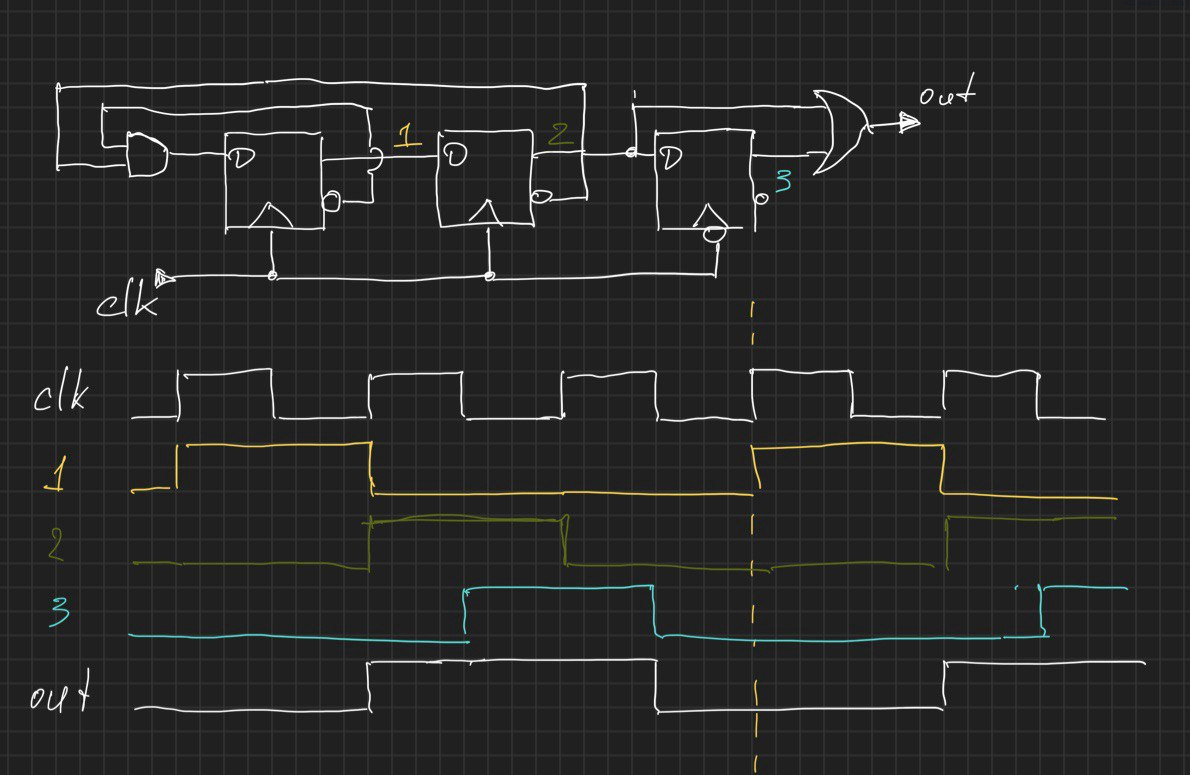

// Code your testbench here

// or browse Examples

`timescale 1ns / 1ns

module testbench();

reg clk;

wire out;

wire qb_dff1;

wire d_dff1;

wire q_dff1;

wire clkb;

wire qb_dff2;

wire d_dff2;

wire q_dff2;

wire qb_dff3;

wire d_dff3;

wire q_dff3;

assign clkb = ~clk;

dff DFF1(.clk(clk), .d(d_dff1), .q(q_dff1), .qb(qb_dff1));

dff DFF2(.clk(clk), .d(d_dff2), .q(q_dff2), .qb(qb_dff2));

dff DFF3(.clk(clkb), .d(d_dff3), .q(q_dff3), .qb(qb_dff3));

and_gate and1(.a(qb_dff1),.b(qb_dff2),.z(d_dff1));

assign d_dff2 = q_dff1;

assign d_dff3 = q_dff2;

or_gate or1(.a(q_dff3),.b(q_dff2),.z(out));

//assign d_dff1 = qb_dff1;

initial begin

$dumpfile("dump.vcd");

$dumpvars(1);

clk = 1'b0;

#18 $finish;

end

always #1 clk = ~clk;

endmodule : testbench result

It is possible of course to not get to the business of the gates, but I am not sure if that is possible to synthesize in reality (not enough experience here heh):

module divide_by_3 (in, out);

input in;

output out;

reg out;

integer temp;

initial begin

out = 1'b0;

temp = 0;

end

always @(posedge in)

begin

temp = temp + 1;

if (temp > 2)

begin

out <= ~out;

temp = 0;

end

end

always @(negedge in)

begin

temp = temp + 1;

if (temp > 2)

begin

out <= ~out;

temp = 0;

end

end

endmodule //divide by 3

Pingback: FPGA Lab: Xcelium simulator tb flow (xrun) | diymicro.org