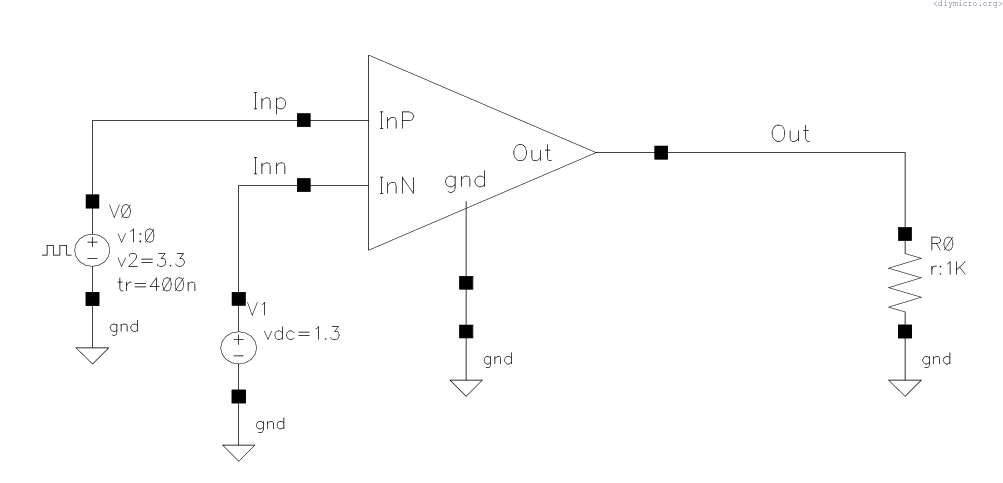

Creating of a comparator model is described below.

What we need from a comparator usually?

- The high level value

- Slew Rate

- Hysteresis

// VerilogA for TBSarge, Comparator, veriloga `include "constants.vams" `include "disciplines.vams" module Comparator(InP, InN, Out, gnd); input InP, InN; output Out; inout gnd; electrical InP, InN, gnd; electrical Out; parameter real Vdd = 3.3; parameter real Hist = 0.05; parameter real Front = 1; integer comptrig; analog begin @(cross(V(InP)-V(InN), +1)) comptrig = 1; @(cross(V(InP)-V(InN)-Hist, -1)) comptrig = 0; V(Out,gnd) <+ transition(comptrig ? Vdd:0, 0, Front); end endmodule

The Slew Rate is defined by rise/fall time, for instance Vdd = 3.3V, edge is 600ns, hysteresis is 500mV.

And the other side:

The hysteresis is here!

The block code is in the bitbucket repo.